Design a 3 Input Xor Gate Using Cmos

Logic gate

This article is about XOR digital logic gate (e.g. SN7486 or CD4030B). For XOR logical operation, see Exclusive or. For other uses, see XOR (disambiguation).

| Input | Output | |

| A | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

XOR gate (sometimes EOR, or EXOR and pronounced as Exclusive OR) is a digital logic gate that gives a true (1 or HIGH) output when the number of true inputs is odd. An XOR gate implements an exclusive or ( ) from mathematical logic; that is, a true output results if one, and only one, of the inputs to the gate is true. If both inputs are false (0/LOW) or both are true, a false output results. XOR represents the inequality function, i.e., the output is true if the inputs are not alike otherwise the output is false. A way to remember XOR is "must have one or the other but not both".

XOR can also be viewed as addition modulo 2. As a result, XOR gates are used to implement binary addition in computers. A half adder consists of an XOR gate and an AND gate. Other uses include subtractors, comparators, and controlled inverters.[1]

The algebraic expressions or or all represent the XOR gate with inputs A and B. The behavior of XOR is summarized in the truth table shown on the right.

Symbols [edit]

There are three schematic symbols for XOR gates: the traditional ANSI and DIN symbols and the IEC symbol. In some cases, the DIN symbol is used with ⊕ instead of ≢. For more information see Logic Gate Symbols.

|  |  | ||

| ANSI XOR Schematic Symbol | IEC XOR Schematic Symbol | DIN XOR Schematic Symbol |

The logic symbols ⊕, Jpq, and ⊻ can be used to denote an XOR operation in algebraic expressions.

C-like languages use the caret symbol ^ to denote bitwise XOR. (Note that the caret does not denote logical conjunction (AND) in these languages, despite the similarity of symbol.)

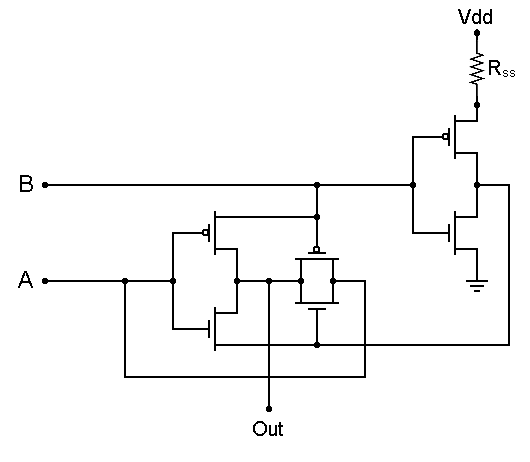

Pass-gate-logic wiring [edit]

An XOR gate can be constructed using MOSFETs. Here is a diagram of a pass transistor logic implementation of an XOR gate.[2] [3] [4] [5] [6]

Transmission Gate Logic wiring of an XOR gate

Note: The "Rss" resistor prevents shunting current directly from "A" and "B" to the output. Without it, if the circuit that provides inputs A and B does not have the proper driving capability, the output might not swing rail to rail or be severely slew-rate limited. The "Rss" resistor also limits the current from Vdd to ground which protects the transistors and saves energy when the transistors are transitioning between states.

Analytical representation [edit]

is an analytical representation of XOR gate:

is an alternative analytical representation.

Alternatives [edit]

XOR gate circuit using three mixed gates

If a specific type of gate is not available, a circuit that implements the same function can be constructed from other available gates. A circuit implementing an XOR function can be trivially constructed from an XNOR gate followed by a NOT gate. If we consider the expression , we can construct an XOR gate circuit directly using AND, OR and NOT gates. However, this approach requires five gates of three different kinds.

As alternative, if different gates are available we can apply Boolean algebra to transform as stated above, and apply de Morgan's Law to the last term to get which can be implemented using only three gates as shown on the right.

An XOR gate circuit can be made from four NAND gates. In fact, both NAND and NOR gates are so-called "universal gates" and any logical function can be constructed from either NAND logic or NOR logic alone. If the four NAND gates are replaced by NOR gates, this results in an XNOR gate, which can be converted to an XOR gate by inverting the output or one of the inputs (e.g. with a fifth NOR gate).

| Desired gate | NAND construction | NOR construction |

|---|---|---|

|  |  |

An alternative arrangement is of five NOR gates in a topology that emphasizes the construction of the function from , noting from de Morgan's Law that a NOR gate is an inverted-input AND gate. Another alternative arrangement is of five NAND gates in a topology that emphasizes the construction of the function from , noting from de Morgan's Law that a NAND gate is an inverted-input OR gate.

| Desired gate | NAND construction | NOR construction |

|---|---|---|

|  |  |

For the NAND constructions, the upper arrangement requires fewer gates. For the NOR constructions, the lower arrangement offers the advantage of a shorter propagation delay (the time delay between an input changing and the output changing).

More than two inputs [edit]

Literal interpretation of the name "exclusive or", or observation of the IEC rectangular symbol, raises the question of correct behaviour with additional inputs. If a logic gate were to accept three or more inputs and produce a true output if exactly one of those inputs were true, then it would in effect be a one-hot detector (and indeed this is the case for only two inputs). However, it is rarely implemented this way in practice.

It is most common to regard subsequent inputs as being applied through a cascade of binary exclusive-or operations: the first two signals are fed into an XOR gate, then the output of that gate is fed into a second XOR gate together with the third signal, and so on for any remaining signals. The result is a circuit that outputs a 1 when the number of 1s at its inputs is odd, and a 0 when the number of incoming 1s is even. This makes it practically useful as a parity generator or a modulo-2 adder.

For example, the 74LVC1G386 microchip is advertised as a three-input logic gate, and implements a parity generator.[7]

Applications [edit]

Example half adder circuit diagram

Example full adder circuit diagram

XOR gates and AND gates are the two most-used structures in VLSI applications.[8]

Uses in addition [edit]

The XOR logic gate can be used as a one-bit adder that adds any two bits together to output one bit. For example, if we add 1 plus 1 in binary, we expect a two-bit answer, 10 (i.e. 2 in decimal). Since the trailing sum bit in this output is achieved with XOR, the preceding carry bit is calculated with an AND gate. This is the main principle in Half Adders. A slightly larger Full Adder circuit may be chained together in order to add longer binary numbers.

Pseudo-random number generator [edit]

Pseudo-random number (PRN) generators, specifically linear-feedback shift registers (LFSR), are defined in terms of the exclusive-or operation. Hence, a suitable setup of XOR gates can model a linear-feedback shift register, in order to generate random numbers.

Correlation and sequence detection [edit]

XOR gates produce a 0 when both inputs match. When searching for a specific bit pattern or PRN sequence in a very long data sequence, a series of XOR gates can be used to compare a string of bits from the data sequence against the target sequence in parallel. The number of 0 outputs can then be counted to determine how well the data sequence matches the target sequence. Correlators are used in many communications devices such as CDMA receivers and decoders for error correction and channel codes. In a CDMA receiver, correlators are used to extract the polarity of a specific PRN sequence out of a combined collection of PRN sequences.

A correlator looking for 11010 in the data sequence 1110100101 would compare the incoming data bits against the target sequence at every possible offset while counting the number of matches (zeros):

1110100101 (data) 11010 (target) 00111 (XOR) 2 zero bits 1110100101 11010 00000 5 zero bits 1110100101 11010 01110 2 zero bits 1110100101 11010 10011 2 zero bits 1110100101 11010 01000 4 zero bits 1110100101 11010 11111 0 zero bits Matches by offset: . : : : : : : : ----------- 0 1 2 3 4 5

In this example, the best match occurs when the target sequence is offset by 1 bit and all five bits match. When offset by 5 bits, the sequence exactly matches its inverse. By looking at the difference between the number of ones and zeros that come out of the bank of XOR gates, it is easy to see where the sequence occurs and whether or not it is inverted. Longer sequences are easier to detect than short sequences.

See also [edit]

- Exclusive or

- AND gate

- OR gate

- Inverter (NOT gate)

- NAND gate

- NOR gate

- XNOR gate

- IMPLY gate

- Boolean algebra

- Logic gate

| | Wikimedia Commons has media related to XOR gates. |

References [edit]

- ^ Fletcher, William (1980). An engineering approach to digital design . Prentice-Hall. p. 98. ISBN0-13-277699-5.

- ^ "Designing combinational logic gates in CMOS". p. 233

- ^ "Transmission Gate XOR".

- ^ "transmission-gate XOR (tiny XOR)" (via [1])

- ^ "Figure 3, Exclusive OR and XNOR gate".

- ^ "Pass-Transistor Logic: Transmission Gate XOR" (p. 11)

- ^ 74LVC1G386 data sheet

- ^ "Comparison of different design techniques of XOR & AND gate using EDA simulation tool".

XOR & AND gates are most important basic building blocks of any VLSI applications.

Design a 3 Input Xor Gate Using Cmos

Source: https://en.wikipedia.org/wiki/XOR_gate

0 Response to "Design a 3 Input Xor Gate Using Cmos"

Postar um comentário